# 通往 PCle 5.0 的快速路徑

將 PCle 4.0 傳輸速率倍增至 32 GT/s

資料中心業者必須採用新一代的技術,來支援 5G 和物聯網所需的響應時間和高頻寬。 未來全球將有數十億個連接到 Internet 的裝置,並執行資料密集型即時應用,屆時 資料中心常見的 100 gigabit Ethernet (GE) 速度 將無法因應如此嚴苛的要求。有鑒於此, 資料中心業者必須將網路速度從 100GE 提高到 400GE。更快的網路速度需要更快的 記憶體和更快的串列匯流排通訊。

在收發器升級到 400GE 的同時,資料中心業者也必須轉換到下一代的高速運算介面。 雙倍資料速率 (DDR) 記憶體將從 DDR 4.0 轉移到 DDR 5.0,而 PCI Express®或 PCIe® 擴展匯流排則將從 PCIe 4.0 轉移到 PCIe 5.0。

PCIe 是一種高速的差動式串列標準,用於資料中心機架的點對點通訊。資料中心業者較傾向把運算任務分配到位於同一機架中的伺服器,以避免不必要的訊務淹沒資料中心網路。PCIe 5.0 標準正在快速發展,因為 PCI 特殊利益團體 (PCI-SIG®)——定義 PCIe 規格的標準機構——計劃在 2019 年完成 PCIe 5.0 標準。

#### PCIe 5.0 的三個重點:

- 為資料中心的 400GE 速度 奠定基礎

- 將 PCle 4.0 的傳輸速率 提高一倍到 32 GT/s

- 帶來新的設計和測試挑戰

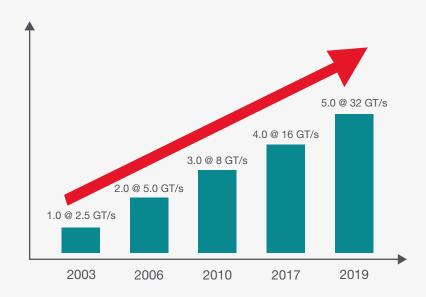

## PCIe 5.0 將 PCIe 4.0 的傳輸速率翻了一倍

新一代 PCIe 標準提供比前一代更多的功能和更快的資料傳輸速率。PCIe 5.0 將 PCIe 4.0 的傳輸速率翻了一倍。PCIe 5.0 的傳輸速率為每秒 32 GT (GT/s),而 PCIe 4.0 支援的傳輸速率為 16 GT/s。PCIe 5.0 具有每秒 64 GB (GB/s) 的單向傳輸頻寬,可提供 128 GB/s 的雙向訊務資料傳輸速率。PCIe 互連技術是許多基於機架層級的資料中心技術開發基礎,例如儲存和圖形處理單元 (GPU)。

圖 1:PCIe 標準的演進

### 只要建構,便可獲得全新網路

儘管 PCI-SIG 計劃在 2019 年完成 PCIe 5.0 標準,但下一代硬體通常需要一年左右的時間才能進入市場。PCIe 5.0 在資料中心的採用取決於對伺服器標準的支援度。儘管如此,晶片組和模組製造商已經開始研發 PCIe 5.0 裝置。

設計人員最關切的問題,是互通性和向下相容性。設計人員需要工具來驗證其設計的參數和協定,以確保效能並符合標準。較高的資料速率會增加信號完整性的問題症狀,例如反射和串擾,進而導致信號衰減和時序問題。較短的時脈週期意味較小的抖動容許量,因此減少 PCIe 5.0 設計中的抖動,遠比前幾代標準要複雜的多。

在實體層、資料鏈路層,和傳輸層都需要 PCIe 測試。

### PCIe 5.0 帶來了新的設計和測試挑戰

設計人員必須在設計週期的早期獲取 PCIe 設計的洞察力。在每個開發階段使用正確的測試解決方案可確保最好的設計品質、符合 PCIe 標準,以及和其他廠商裝置的互通性。工程師須藉由量測參考時脈和資料信號來驗證 PCIe 效能。

對於板卡機電 (CEM) 規格,PCI-SIG 提供相容性測試卡 (CBB)、相容性負載卡 (CLB) 和 SigTest 軟體,以進行電氣相容性測試。PCIe 裝置必須成功通過「標準測試流程」測試,其涵蓋所有 PCI-SIG SigTest 軟體測試,在 PCI-SIG 測試大會上使用官方 PCI-SIG 認可的測試夾具進行。在參加測試大會之前,設計人員使用提供完整 PCIe 標準支援的測試工具,可確保其 PCIe 裝置將通過所有相容性測試。

#### PCIe 測試解決方案 可確保:

- 最好的設計品質

- 符合 PCIe 標準

- 和其他廠商裝置的 互通性

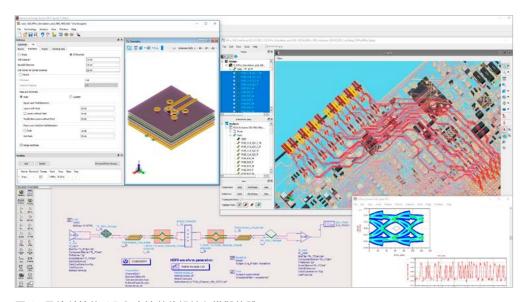

### PCIe 設計與模擬

當資料速率增加,設計高速串列資料鏈路會明顯變得更為複雜。通道拓撲會變得更多樣化,而主動元件也會有更多的參數需要調整。模擬 PCIe 設計的信號和電源完整性最佳化,並分析高速積體電路 (IC) 封裝和印刷電路板 (PCB) 互連等元件的電磁 (EM) 效應。使用設計和模擬工具,設計人員可以在第一個原型之前,快速有效地評估所有 PCIe 鏈路的端到端效能,進而避免代價高昂的重新設計週期。

圖 2:是德科技的 ADS 高速數位設計和模擬軟體

#### PCIe 發射器測試

特定類型的不相關抖動值是 PCIe 發射器測試中主要處理的問題。對於超過 8 GT/s 的 PCIe 速度,PCIe 接收器可利用強大的等化特性。雖然等化器能夠補償資料相依抖動,但 PCIe 標準指定的參考接收器等化,無法充分補償不相關的發射器抖動。使用能夠解決不相關抖動的測試工具,可確保 PCIe 發射器設計的效能。

#### PCIe 接收器測試

在 PCIe 5.0 的 32 GT/s 速度下,要從 PCIe 信號中萃取數位內容變得更具挑戰性。在這樣的高資料傳輸速率下,PCIe 接收器會因通道的高頻損耗特性,而經常接收到嚴重劣化的信號,導致不可接受的誤碼率 (BER)。必須使用可恢復傳輸信號品質的等化技術,來設計並驗證能夠容忍這些失真信號的穩健接收器。PCIe 5.0 最多支援達 16 個通道的規格,進一步使接收器設計和除錯變得更為複雜。一個強大的 PCIe 接收器測試解決方案可實現測試自動化,將測試時間從數天縮短到數小時。

# PCIe 互連測試

該通道是 PCIe 系統的關鍵元素之一,通道中有許多失真源會降低從 PCIe 發射器傳送到 PCIe 接收器的信號品質,例如串擾、抖動和符碼間干擾 (ISI) 等等。您必須量測通道中的損耗特性,確保它們在 PCIe 針對給定資料速率所定義的限制範圍內。散射參數 (S 參數) 可用於分析高頻電路,例如 PCIe 系統中的通道。在 PCIe 設計快速驗證參數方面,確保其符合 PCIe 規格定義的效能要求,是測試過程的重要部分。

#### PCIe 協定測試

您需在實體層、資料鏈路層和交易層進行協定驗證。除了強制性的協定相符性測試外, PCI-SIG 還建議執行了1百多項額外的測試,以便準確分析 PCIe 設計。鏈路訓練和狀態 機 (LTSSM) 是協定測試的關鍵。

鏈路訓練可確保資料封包在鏈路夥伴之間可靠地傳輸。因此需要使用協定分析和訓練器工具,來確定 PCIe 裝置是否能夠成功地與鏈路夥伴進行通訊。PCIe 協定測試工具可讓工程師執行複雜的協定測試,並快速對任何檢測錯誤進行除錯,以確保 PCIe 裝置的相容性。

## 結語

PCIe 標準是讓資料中心伺服器周邊設備彼此互連的核心技術。PCIe 5.0 是該標準的最新版本,可為 16 個通道系統提供大約 128 GB/s 的全雙工頻寬,使得資料中心能夠大規模採用 400GE 技術。藉由選擇正確的測試工具進行設計、模擬、分析和驗證,可確保 PCIe 裝置能夠無縫通過所有必須的相容性測試,更快進入市場。

有關是德科技 PCIe 5.0 設計和測試挑戰解決方案的詳細資訊,請瀏覽下列網頁:

- 想加快 Gigabit 數位設計的上市時間,請查看高速數位系統設計

- 想瞭解有關模擬、分析和驗證 PCIe 設計測試解決方案的詳細資訊,請查看 PCI Express (PCIe) 設計與測試

PCI-SIG®、PCIe®和 PCI Express®是 PCI-SIG 的註冊商標和服務商標。

# 詳細資訊,請上網查詢:www.keysight.com

有關是德科技電子量測產品、應用及服務的詳細資訊,可查詢我們的網站或來電洽詢是德科技聯絡窗口:www.keysight.com/find/contactus